數字集成電路靜態時序分析基礎 筆記⑥ 集成電路設計中的時序收斂

引言:從分析到設計

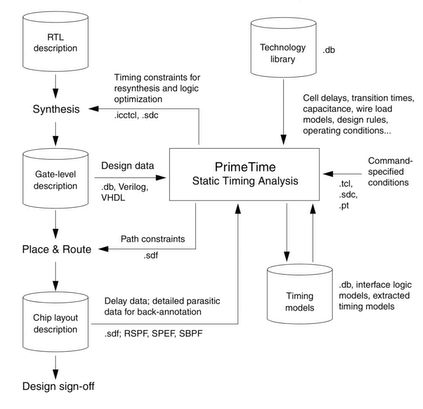

在完成了對建立時間、保持時間、時鐘網絡、時序路徑等基礎概念的剖析后,我們的筆記系列最終要回歸到 集成電路設計 這一核心目標上。靜態時序分析(STA)并非一個孤立的驗證環節,而是貫穿于整個設計流程的指導性原則與關鍵保障。本筆記將探討如何將STA理論應用于實際設計,以實現 時序收斂 —— 即確保設計在所有工藝角、電壓和溫度(PVT)條件下都能滿足預設的時序要求。

一、 設計流程中的STA介入點

一個典型的數字IC設計流程中,STA是多次迭代進行的:

- 綜合階段(邏輯綜合):在將RTL代碼映射到目標工藝庫的門級網表后,即進行初始的STA。此時主要關注組合邏輯路徑的延遲,通過優化邏輯結構、選擇驅動能力合適的單元來初步滿足時序約束。

- 布局階段:初步的單元擺放后,可以利用線負載模型進行更精確的時序估算。此時的時序違例主要依靠調整布局、優化高扇出網絡來修復。

- 時鐘樹綜合(CTS)后:這是STA的關鍵節點。時鐘網絡的實際RC參數確定后,需要進行 帶時鐘樹信息的STA,重點檢查時鐘偏斜、建立時間和保持時間。此時的保持時間違例會大量出現,需要通過插入緩沖器來修復。

- 布線后:提取實際的寄生參數(RC),進行 簽核STA。這是最精確、最嚴苛的分析,是芯片流片前的最終時序保障。任何在此階段發現的違例都必須修復。

二、 時序約束的制定:設計的“指揮棒”

STA的準確性極度依賴于 時序約束文件(SDC文件)的完整性。它定義了設計的時序目標,主要包括:

- 時鐘定義:創建時鐘(周期、占空比、源點)、生成時鐘、時鐘組、時鐘不確定性。

- 輸入/輸出延遲:定義端口外部世界的時序關系,是分析I/O路徑的基礎。

- 時序例外:設置虛假路徑、多周期路徑,避免過度優化,節省面積與功耗。

- 最大/最小延遲約束:對特殊路徑進行定制化約束。

關鍵點:不完整或錯誤的約束會導致STA結果失真,要么掩蓋真正的時序問題(導致流片失敗),要么對非關鍵路徑進行過度優化(導致面積功耗浪費)。

三、 實現時序收斂的核心技術與策略

當STA報告顯示時序違例(Slack為負)時,設計者需要采取一系列優化手段:

- 針對建立時間違例的優化:

- 邏輯重組:將關鍵路徑上的復雜邏輯分解或重組,減少級聯邏輯的深度。

- 尺寸調整:增大關鍵路徑上驅動單元的尺寸(以增加驅動能力,減少本級延遲),或減小其負載單元的尺寸(以減少負載電容)。

- 寄存器重定時:在流水線中移動寄存器的位置,平衡組合邏輯延遲。

- 使用低閾值電壓(LVT)單元:在關鍵路徑上使用速度更快但漏電較大的單元,需謹慎權衡功耗。

- 優化時鐘網絡:減少關鍵路徑的時鐘延遲(局部優化),或調整時鐘偏斜以幫助特定路徑。

- 針對保持時間違例的優化:

- 插入延遲緩沖器:在數據路徑上插入緩沖器以增加最小路徑的延遲,這是最常用的方法。

- 減小驅動能力:將過快路徑上的驅動單元換為尺寸更小的版本,增加其本征延遲。

- 使用高閾值電壓(HVT)單元:在非關鍵路徑上使用速度較慢但漏電小的單元,可以自然增加延遲。

- 調整時鐘偏斜:在合法范圍內,適當增加捕獲時鐘的延遲(對發射時鐘)。

重要原則:建立時間違例的修復通常以增加面積和功耗為代價;而保持時間違例的修復通常以增加面積和微小幅度的功耗為代價。修復過程中需避免“拆東墻補西墻”。

四、 先進工藝下的時序挑戰

隨著工藝節點進入深亞微米,時序分析變得更加復雜:

- 互連延遲主導:線延遲遠超門延遲,使得物理設計與時序分析必須緊密結合(時序驅動布局布線)。

- 工藝變異:片上變異、線邊緣粗糙度等要求進行更復雜的 統計靜態時序分析,而不能僅依賴角落分析。

- 信號完整性:串擾、電壓降會顯著影響單元延遲,必須進行帶噪聲和電源完整性的STA。

- 多模態多角落分析:設計需要在多種工作模式(功能模式、測試模式、省電模式)和數十個甚至上百個PVT條件下同時滿足時序,分析量巨大。

五、 STA——設計與制造的橋梁

靜態時序分析是現代數字集成電路設計的基石。它從最初RTL代碼的綜合指導,到最終簽核驗證,全程為設計“保駕護航”。理解STA,不僅僅是掌握工具命令,更是深入理解 時序模型、電路行為與物理實現 之間的深刻聯系。一個優秀的設計工程師,必須能夠:

- 編寫正確完備的時序約束;

- 解讀復雜的STA報告,精準定位瓶頸;

- 運用多種策略,在時序、面積、功耗之間做出最佳折衷;

- 預見先進工藝帶來的新挑戰,并理解相應的分析流程。

至此,《數字集成電路靜態時序分析基礎》系列筆記完結。希望這六篇筆記能為你構建一個清晰、堅實的STA知識框架,助你在集成電路設計的道路上走得更穩、更遠。

如若轉載,請注明出處:http://m.ycbgl.cn/product/43.html

更新時間:2026-04-10 07:08:22