集成電路設(shè)計 從藍(lán)圖到現(xiàn)實(shí),技術(shù)與資源的交匯點(diǎn)

集成電路(IC)設(shè)計是現(xiàn)代電子工業(yè)的基石,它決定了從智能手機(jī)到航天器幾乎所有電子設(shè)備的性能和功能。這一過程將抽象的電路邏輯轉(zhuǎn)化為可在硅片上精確制造的物理布局,是一個高度復(fù)雜、多學(xué)科交叉的工程領(lǐng)域。

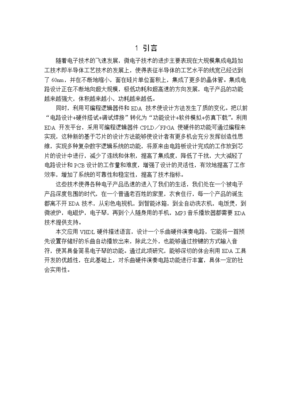

集成電路設(shè)計的核心流程

典型的集成電路設(shè)計流程始于系統(tǒng)規(guī)格定義,明確芯片的功能、性能、功耗和成本目標(biāo)。隨后進(jìn)入架構(gòu)設(shè)計階段,規(guī)劃芯片的整體模塊劃分和數(shù)據(jù)流。

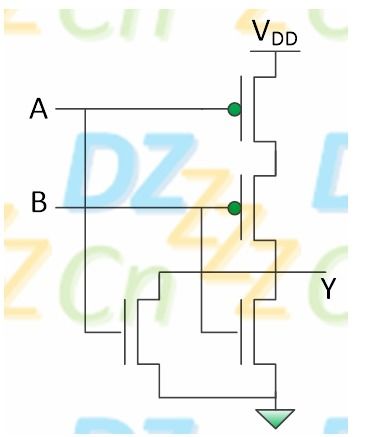

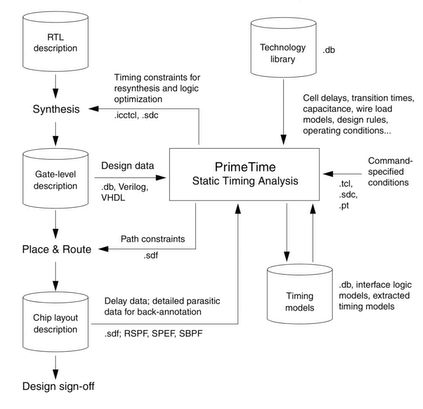

接下來是關(guān)鍵的前端設(shè)計,也稱為邏輯設(shè)計。設(shè)計師使用硬件描述語言(如Verilog或VHDL)編寫代碼,描述芯片的邏輯功能。通過仿真和驗證確保邏輯正確后,會進(jìn)行邏輯綜合,將代碼轉(zhuǎn)換為由基本邏輯單元(如與門、或門)組成的網(wǎng)表。

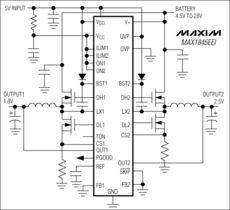

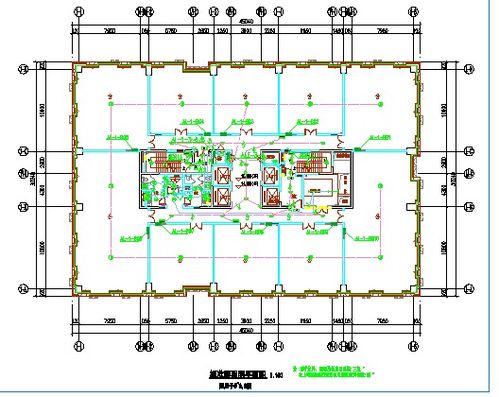

然后是更為復(fù)雜的后端設(shè)計,即物理設(shè)計。這一階段將邏輯網(wǎng)表映射到實(shí)際的硅片布局上,包括布局規(guī)劃、單元放置、時鐘樹綜合、布線等步驟。設(shè)計師必須綜合考慮時序、功耗、信號完整性和制造工藝規(guī)則,確保最終設(shè)計能夠被成功生產(chǎn)。

設(shè)計圖紙與資源的獲取

提及“某住宅區(qū)集成電路設(shè)計施工圖紙免費(fèi)下載”,這里可能存在概念的混淆或信息的特殊性。通常,集成電路的物理設(shè)計成果是高度機(jī)密的GDSII格式文件,它是芯片制造的“施工藍(lán)圖”,包含了每一層掩模的精確幾何圖形。這類核心知識產(chǎn)權(quán)文件極少公開,更不會免費(fèi)提供。

對于學(xué)習(xí)和研究而言,業(yè)界存在寶貴的開源資源:

- 開源IP核與設(shè)計:如RISC-V處理器核、OpenCores平臺上的各種設(shè)計,提供了可研究、可修改的硬件描述語言源碼。

- 開源PDK與設(shè)計套件:谷歌與SkyWater合作推出的開源工藝設(shè)計套件,允許設(shè)計者使用真實(shí)的制造工藝規(guī)則進(jìn)行實(shí)踐。

- 教育機(jī)構(gòu)資源:一些大學(xué)課程會提供簡化后的設(shè)計案例和教程供學(xué)生學(xué)習(xí)。

獲取這些資源,應(yīng)前往上述官方開源平臺、專業(yè)學(xué)術(shù)站點(diǎn)或可靠的電子設(shè)計自動化(EDA)工具教育版頁面,而非在非專業(yè)的住宅區(qū)網(wǎng)絡(luò)信息中尋找,后者可能存在安全風(fēng)險或信息謬誤。

未來趨勢與挑戰(zhàn)

隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度,集成電路設(shè)計面臨著功耗墻、工藝變異、設(shè)計復(fù)雜度爆炸等巨大挑戰(zhàn)。也涌現(xiàn)出新的機(jī)遇:

- 異構(gòu)集成與Chiplet:將不同工藝、功能的芯片粒通過先進(jìn)封裝集成,提升設(shè)計靈活性。

- AI驅(qū)動的EDA工具:利用機(jī)器學(xué)習(xí)優(yōu)化布局布線,大幅提升設(shè)計效率。

- 開源生態(tài)的壯大:降低先進(jìn)芯片的設(shè)計門檻,促進(jìn)創(chuàng)新。

###

集成電路設(shè)計是一座連接抽象創(chuàng)意與物理實(shí)體的精密橋梁。雖然核心的“施工圖紙”屬于企業(yè)最高機(jī)密,但蓬勃發(fā)展的開源硬件運(yùn)動和豐富的教育資源,為每一位有志于踏入此領(lǐng)域的學(xué)習(xí)者敞開了大門。理解其基本原理,善用合法開放的工具與資源,是掌握這門尖端技術(shù)的正確起點(diǎn)。

如若轉(zhuǎn)載,請注明出處:http://m.ycbgl.cn/product/45.html

更新時間:2026-04-10 13:04:01